SD卡学习(SDIO和SPI模式)* * SD卡的操作模式:SD卡模式(SDIO)、SPI模式(默认为SD模式)。其中SD卡模式的信号线有:CLK、CMD、DAT0-DAT3,6根线。SPI模式的信号线有:CS、CLK、MISO(DATAOUT)、MOSI(DATAIN),4根...

”axi ps读写pl“ 的搜索结果

博客配套源码工程 https://blog.csdn.net/botao_li/article/details/95302992

对于FPGA编程时的v文件中的寄存器,在SDK编程时需要一些读写操作,以实现PS与PL部分的信息交换。下面用一具体例子记录所需要的步骤 。如若有误请指正。首先需要将v文件代码封装为带有AXI总线的IP,才能实现PS与PL的...

zynq pl通过axi总线读写ps端ddr,没有使用dma,完整程序压缩包

ZYNQ_PS读写PL资源

标签: zynq

PL 和 PS 的高效交互是 zynq 7000 soc 开发的重中之重,我们常常需要将 PL 端的大量数 据实时送到 PS 端处理,或者将 PS 端处理结果...线来读写 PS 端 ddr 的数据,这里面涉及到 AXI4 协议,vivado 的 FPGA 调试等。

PL 和PS的高效交互是zynq 7000 soc开发的重中之重,我们常常需要将PL端的大量数 据实时送到PS端处理,或者将PS端处理结果实时送到PL端处理,常规...线来读写PS端ddr的数据,这里面涉及到AXI4协议,vivado的FPGA调试等。

如题:详细链接:https://blog.csdn.net/LOTOOHE/article/details/78692798

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将结果打印输出到串口终端显示。 涉及到AXI BRAM ...

另一个好像传错了,这是主要的ip,sdk的代码在博客中已经给出,https://blog.csdn.net/LOTOOHE/article/details/78692798

PL 和 PS 的高效交互是 zynq 7000 soc 开发的重中之重,常常需要将 PL 端的大量数据实时送到 PS 端处理,或者将 PS 端处理结果实时送到 PL 端处理,但是各种协议非常麻烦,灵活性也比较差,直接通过 AXI 总线来读写 ...

前面已经详细介绍了从PL端如何用AXI总线去控制DDR的读写,并且从AXI_BRESP的返回值来看,我们也是成功写入了的。但是没有通过别的方式来验证写入的数据的话,总是感觉差了点什么。今天试了一把从PS端直接读取DDR里面...

说起PS、PL数据交互,常见的有IO方式:MIO EMIO GPIO,还有利用BRAM或FIFO等,在上一篇文章ZYNQ学习笔记(三):PL与PS数据交互—— UART串口+AXI GPIO控制DDS IP核输出实验咱们学会了如何利用AXI GPIO IP核来实现PS...

ZYNQ7000系列中PS端与PL端的通信都是通过AXI总线进行连接的,利用好AXI协议是PS与PL交互的基础,因此设计这个实验来进一步了解两者间的通信。1.实验目的PL端通过AXI协议访问PS端的DDR内存,其中包括往DDR写数据,...

如果PS与PL端进行数据交互,可以直接设计PL端为从机,PS端向PL端的reg写入数据即可,但是对于图像处理等大数据量的数据交互来说,PL端的BRAM毕竟容量有限,很难用BRAM作为两者间的数据缓存器。对于这样的应用来说,...

参见我的工程E:\vivado_program\ps_control_pl_ddr3该例程是在ZC706开发板上实现的,在vivado中如下所示:其中mig的配置比较复杂,具体参考文档在如下下载页中下载:...在SDK中的程序如下所示:#include &...

本文是PL读写DDR3 实现PS和PL间的数据交互的继续,深入分析其代码。 首先分析基本要求,或者需求分析,然后代码分析,这个代码是上文中利用vivado 2018.2 自动生成的,也许做了一点修改比如注释。然后对代码分段...

环境:vivado2018.3 芯片: xc7z100ffg900-2 ... 实验目的:将ADC接收的数据先存入DDR3,待PS端读取完成后,再存入一批。 1、工程规划 ...DDR芯片的管脚是绑定到Zynq的DDR接口上的。...而Zynq系统的这个DDR总线接口有是...

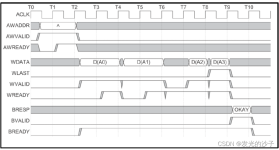

本文是PL读写DDR3 实现PS和PL间的数据交互以及PL读写DDR3 实现PS和PL间的数据交互 代码分析的继续 虽然在代码分析一文中分析了代码,但还是时序波形图比较直观,我这是用Vivado的集成逻辑分析仪ILA 在有sdk 下的...

本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中 加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。 以下为本实验原理图,CPU通过AXI BRAM Controller读取BRAM数据,...

现在终于开始正式准备读写DDR了,开发环境:VIVADO2014.2 + SDK。 一、首先要想在PL端通过AXI去控制DDR,我们必须要有一个AXI master,由于是测试,就不自己写了,直接用package IP生成,方法如下: ...

其打开流程,包括打开Excel程序、打开Excel文件以及打开sheet;表示已写入的区域,其对应的行数和列数就比较有代表性,根据这两个值进行循环,就可以把刚刚写入的数据打印出来了。这里需要建立起对Excel中数据组织的...

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将结果打印输出到串口终端显示。涉及到AXI BRAM ...

PL是怎样访问DDR的?zynq-7000的地址映射,PL作为主设备访问ddr时所用的地址是0x40000000-0x7FFFFFFF;所以在搭建环境的时候要注意pl所给的地址为0x40000000-0x7FFFFFFF才能访问到PS的DDR。另外值得注意的是Dcache的...

PS部分使用AXI-LITE去读取PL部分采样到的AD值,如果整个电路只包含一个AXI-lite IP,里面只含一个ADS7825的采样时序,那么PS读取到的AD值通过UART打印出来是正确的,但是另外又加入了一个DAC的AXI-lite IP后,读取到...

推荐文章

- Java面向对象程序设计 第七章总结_方法的返回值被错误地处理为一个非空的对象-程序员宅基地

- RFX2401C skyworks射频2.4GHZ ZIGBEE/ISM发射/接收RFeIC_rfx2401c csdn-程序员宅基地

- Lambda简便方法引用、构造方法引用_lambdautils.getname-程序员宅基地

- sql表格模型获取记录内容_SQL Server和BI –如何使用Excel记录表格模型-程序员宅基地

- GateWay配置_grateway配置-程序员宅基地

- 云栖专辑| 阿里毕玄:程序员的成长路线-程序员宅基地

- Android 导出traces.txt 遇到的坑_biotraces无法导出-程序员宅基地

- 【ffmpeg 给视频添加背景音乐,去掉视频背景音乐原声】_ffmpeg.net 视频 加入 音频-程序员宅基地

- cocos2d-x3.2 lua 返回键监听_cocos2dx-lua cc.director:getinstance():endtolua()-程序员宅基地

- etcc oracle ebs,Oracle EBS12.2.6 克隆问题集合-程序员宅基地